Compliant and efficient development of airborne FPGAs and ASICs

The complexity of ASIC and FPGA-based airborne electronic hardware (AEH) is constantly increasing. Verification activities must ensure that HDL and netlist models correctly implement the hardware requirements, while also being efficient, complete and, crucially, compliant with the DO-254 standard. Formal solutions complement traditional verification methods, and are very effective in the quick and early detection of corner-case and random errors that could be missed by simulation tests. Formal verification tools have reached widespread adoption in the semiconductor industry, particularly for ASICs, and in safety-critical applications. Over the past ten years, industry partnerships and technology developments have removed the usability and pricing barriers to the deployment of formal tools in FPGA design flows.

This presentation focuses on the formal verification solutions that can provide high ROI in AEH development projects. These solutions reduce the risk of undetected hardware issues, and enable a more predictable and efficient path to airworthiness certification.

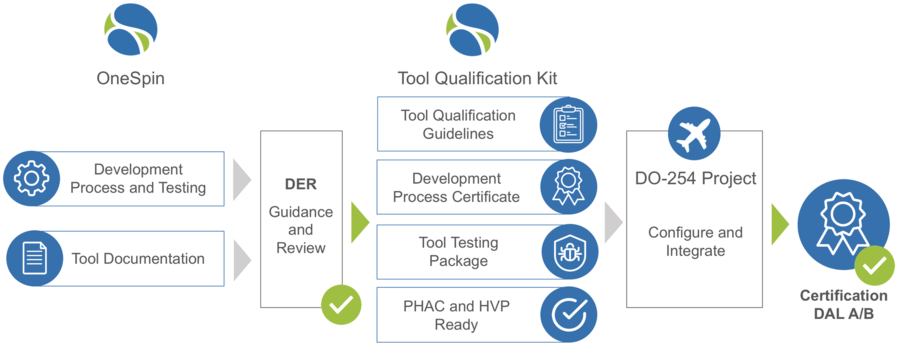

Tool Qualification for Functional Safety Compliance

DO-254 and DO-330

Software tools applied in the development of AEH must undergo tool assessment and qualification to comply with relevant functional safety standards. OneSpin provides expert support to reduce the qualification efforts for its family of formal tools. In addition, OneSpin 360 EC-FPGA, a sequential equivalence checking tool to automate the verification of synthesis and other implementation steps, features an optional DO-254 tool qualification kit (TQK) (see press release). The DO-254 TQK enables OneSpin users to meet the highest aviation electronic systems requirements for AEH set by DO-254 (DAL A/B) with minimal effort.