## DATASHEET **OneSpin**® **360 DV-SC**<sup>™</sup> SystemC/C++ Extension to OneSpin 360 DV<sup>™</sup>

## FORMAL VERIFICATION OF ALGORITHMIC AND HIGH LEVEL SYNTHESIS MODELS

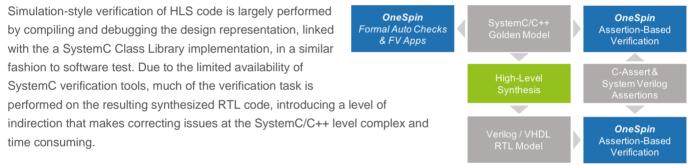

High-Level Synthesis (HLS) transforms algorithmic and potentially untimed design models often written in SystemC and C++ to fully timed Register Transfer Level (RTL) design blocks. The primary verification requirement is to allow thorough verification of algorithmic code prior to synthesis, in order to ensure that the abstract algorithm implementation is tested and fully optimized against the original specification, as well as avoiding long debug cycles.

# OneSpin's SystemC/C++ Extension to OneSpin 360 DV enables formal verification for easy bug detection and functional verification of SystemC/C++ code.

| Automatic Formal Analysis                                                                                                                        |  | Tool Guided Verification                                                                              |  | Assertion Based Verification                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|

| <b>DV-Inspect</b><br>Structural Analysis & Linting<br>Initialization & Reset<br>Safe Coding<br>Activation & Reachability<br>Arithmetic Precision |  | DV-Verify Apps<br>UMR & X-Propagation<br>Protocol Verification IP<br>Scoreboard<br>Design Exploration |  | <b>DV-Verify Formal ABV</b><br>SV-Assertions, C-Assert<br>Cover Points<br>Observation Coverage |

|                                                                                                                                                  |  |                                                                                                       |  |                                                                                                |

| Easy Adoption & Increasing Value                                                                                                                 |  |                                                                                                       |  |                                                                                                |

Coding issues, such as use of undefined values from uninitialized memory reads, or undefined operation results (e.g. division by zero), race condtions between threads, as well as SystemC-specific automated arithmetic overflows, and number precision problems may be

effectively detected using **OneSpin 360 DV-Inspect™** formal auto checks. Automated **DV-Verify Apps** at the SystemC/C++ level, allow thorough functional analysis, e.g. for data flow integrity. Support for C-Assert and temporal (with timing) System Verilog Assertions (SVA) as part of **DV-Verify Formal ABV** enables full assertion-based formal verification, including popular coverage metrics such as Quantify<sup>™</sup> observation coverage. OneSpin 360 DV-SC works with major high level synthesis tools like Cadence Stratus<sup>™</sup> including Stratus SystemC IP library (cynw\*) and NEC Cyber-Workbench<sup>™</sup>, as well as C/C++ code generated from Matlab/Simulink<sup>™</sup>. A versatile debugger and analyzer targeted at SystemC is integrated in the tool.

### **ONESPIN 360 DV-SC FEATURE OVERVIEW**

#### SYSTEMC/C++ LANGUAGE

- Generic C/C++ with static memory layout, and static polymorphism, including pointers, fixed sized arrays, structs, classes, templates

- Standard Synthesizable SystemC, including sc\_fixed with QM\_TRM and QM\_WRAP

- Models for HLS, such as Cadence Stratus<sup>™</sup>, including Cadence Stratus<sup>™</sup> Synthesis cynw\* libraries, and NEC Cyber-Workbench<sup>™</sup>

- Algorithmic C/C++ models without floating point types,

e.g. generated from Matlab/Simulink<sup>™</sup>

- Mixed Language with Verilog/System Verilog/VHDL

#### FORMAL AUTO CHECKS / SUPER LINTING

- Initialization/Reset Checks

- Arithmetic Overflow and Precision Checks for SystemC sc\_int, sc\_uint, sc\_fixed/sc\_ufixed, Cadence cynw\_fixed/cynw\_ufixed, and C++ base types (e.g. uint8\_t)

- Range and condition Checks, e.g. array access out of bounds, division by zero

- Race detection between threads, e.g. write-write races

#### FORMAL COVERAGE ANALYSIS

- Dead Code detection, line/block coverage

- FSM deadlock detection, state/transition coverage

#### **ONESPIN SOLUTIONS**

- Generation of SystemC and System Verilog test

benches

- Design consistency checking between SystemC/C++ and RTL

#### FORMAL APPS

- Uninitialized Memory Read (UMR) Checks and X-Propagation Checks

- Interface Protocol Checks using Verification IP, e.g. ARM APB/AHB/AXI

- Data-Flow analysis using Scoreboard Verification IP

- Connectivity Verification

#### FORMAL ASSERTION BASED VERIFICATION

- C-Assert, System Verilog Assertions, OneSpin TiDAL<sup>™</sup> SVA

- Quantify™ Formal Observation Coverage

#### INTEGRATED DEBUGGER & ANALYSER

- Waveform Debugger, Source Code Debugger, Design Instance / Hierarchy Browse

- Fan-in / Fan-out / Driver Tracing through source code

- Active Value and Active Code Annotation

- Native Value Annotation for SystemC and cynw data types, e.g. fixed point data type

OneSpin Solutions is a pioneer of advanced, award winning formal verification technologies, incubated at Infineon and leveraging 300+ engineering years of development and applications experience. The company's product line includes automated design analysis requiring no knowledge of formal methods, to powerful, exhaustive, coverage-driven property verification, and incorporates an Equivalency Checker used as a gold standard within other design tool development programs. Excelling in ease-of-use, high-performance and accessibility, OneSpin's products have been leveraged by a large number of electronic system and semiconductor companies worldwide on many leading edge designs. The company operates globally, with its headquarters in Munich, Germany, and offices in San Jose, CA and Tokyo, Japan.

## YOUR NOTES:

Contact · info@onespin.com · www.onespin.com USA: +1 408 734 1900 · Europe: +49 89 99013-0 · Japan: +81 3 4530 3865

© Copyright 2016 OneSpin. All rights reserved. OneSpin is a registered trademark of OneSpin Solutions GmbH. OneSpin Solutions, OneSpin 360, the 360 EC product names, the OneSpin logo are trademarks of OneSpin Solutions GmbH. All other trademarks are the property of their respective owners.