5Gワイヤレス、IoT、AIアプリケーションなどに使用される、複雑なSoCプラットフォームの徹底した検証

アーキテクチャやICテクノロジにおけるあらゆるイノベーションは、機能検証プロセスにさらなるプレッシャーを与えます。ヘテロジニアスコンピューティングプラットフォームの新たな世代は、またしても検証のハードルを高めています。この新しいアプローチは、デバイス開発者とチップユーザーの双方が取り組まなければならない新しい課題を生み出しています。

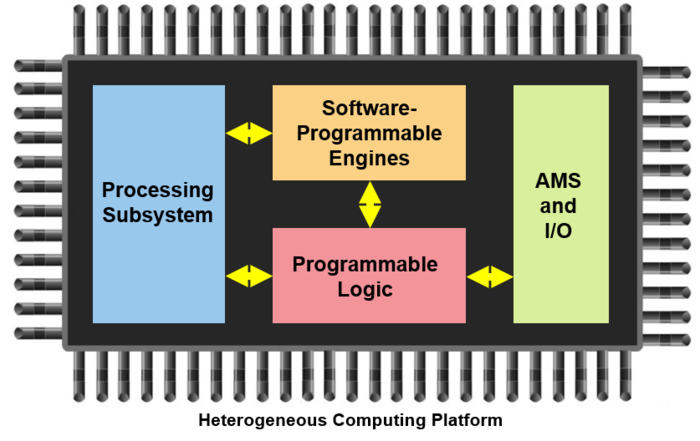

システムオンチップ(SoC)設計には、しばらく前からすでにヘテロジニアスプロセッサが含まれています。従来型のCPUはマルチプロセッササブシステムに成長する一方、GPUやその他の特化した計算エンジンも同じチップに搭載されるようになりました。しかしながら、ヘテロジニアスコンピューティングプラットフォームにはFPGAタイプのプログラマブルロジックとソフトウェアプログラマブルエンジンの両方が含まれ、このアーキテクチャをさらに2歩進化させています。これらの機能はユーザーが希望する機能をハードウェア、ソフトウェア、あるいはその組み合わせに実装できる柔軟性を各段に向上させました。

ヘテロジニアスコンピューティングプラットフォームはそのパワーと幅広い用途への適合性によって、IC業界において人気のある重要なセグメントとなるでしょう。機械学習、深層学習、5Gワイヤレスといったアプリケーションは、この新しいアーキテクチャと野心的な7nmプロセスノードから恩恵を受けると思われます。その他関連のあるアプリケーション分野には、防衛/航空宇宙、自律走行車、クラウドコンピューティング、IoT(Internet of Things)が含まれるでしょう。ヘテロジニアスコンピューティングICの複雑性はさまざまな検証課題に直結しています。この問題にはいくつかの側面があります。

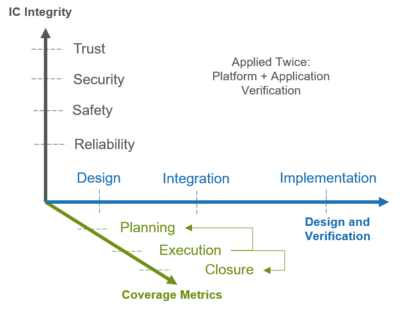

まず根本的な問題は、いかなるプログラマブルチップも2度検証しなければならないということです。まずデバイス開発者とベンダーによって、そして特定のアプリケーションのユーザーによってです。標準的なICや従来のASICは1度検証され、そして製造されていました。FPGAやSoCは、チップの意図されるアプリケーションのコンテキストにおいてユーザーが再検証しなければなりません。ヘテロジニアスコンピューティングプラットフォームには、FPGAの持つすべてのハードウェア検証の複雑性が伴うだけでなく、プロセシングサブシステムを持つことから組み込みコンピューティングのあらゆるハードウェア/ソフトウェア検証の複雑性も存在します。

機能的信頼性を確保するには、個別のブロックの徹底した検証、ブロックの相互接続の検証、そしてインプリメンテーションが意図された機能を保っていることを確認することが必要です。OneSpinの機能信頼性ソリューションは、画期的なフォーマル技術を活用した多数のツールやアプリによって、検証のあらゆる側面をカバーしています。例としては、DV-Inspect™による自動チェック、さまざまなアプリによる自動化されたフォーマル解析、そしてDV-Verify™による各種アサーションベース検証機能があります。フォーマル検証の網羅的なパワーを活用することで、カバレッジクロージャを格段に早期に達成できます。

その他、フルチップインテグレーション検証のためのアプリもあります。たとえばConnectivity XLは、最大規模のヘテロジニアスコンピューティングICに使用される百万以上のトップレベル接続パスを検証することができます。主要なサブシステム間の相互接続は、多くの場合コンフィギュラブルであり非常に複雑です。RTL設計が完全に検証された後、OneSpinのEC-ASIC™ とEC-FPGA™ はフォーマル等価性チェックを使用して、合成と配置配線によるインプリメンテーションが設計の機能を変更していないことを確認することができます。

機能正確性以外にも、ヘテロジニアスコンピューティングプラットフォームのアプリケーションの多くには厳密な安全性、セキュリティ、信頼性の要件があります。OneSpinの機能安全性ソリューションは、ハードウェアとソフトウェアの安全性メカニズムが、アルファ粒子衝突などのランダムエラー発生時にも正しく動作することを検証します。このプロセスには、自動車、航空宇宙、産業用装置などの主要なアプリケーションの安全規格で必要とされるハードウェアメトリックの計算も含まれています。

OneSpinの信頼性およびセキュリティソリューションは、悪意あるロジックまたはハードウェアトロイなどが設計フローのいかなる段階においても挿入されていないことを検証するとともに、設計そのものの持つセキュリティ脆弱性も検知します。フォーマル技術はこうした検証に理想的です。意図した機能に対するカバレッジの完全性、ならびに悪意ある人物によって挿入されたあるいは設計ツールのエラーにより入り込んだ不要なロジックが存在しないことを検証できるのは、フォーマル技術だけだからです。フォーマル技術により、ヘテロジニアスコンピューティングプラットフォームがサポートする要求の厳しいアプリケーションに向けた、完全に設計、検証、実装済みのICを完成することができます。

OneSpinのRISC-V Integrity Verification Solutionは、IPコアインプリメンテーションがするべきことをすべて行い、するべきでないことをまったく行わないことを保証するものです。これにより、SoC設計者は RISC-V コアが ISA仕様に準拠していることに自信を持ってライセンスできます。また IP ベンダーは自社独自のエコシステムをサポートしながら、エコシステム利用者も正しく準拠させることができます。さらに、SoC設計者は RISC-V ISA にカスタム機能を追加して特定のアプリケーションをサポートすることもできます。OneSpinのソリューションは、機能を追加しても何も壊れないことを保証し、また新しい機能を検証するのにも十分な柔軟性を備えています。

More information…

OneSpin’s Operational SVA enables formal verification enthusiasts to develop high-level, non-overlapping assertions that capture end-to-end transactions and requirements in a concise, elegant way.

»Learn more…The OneSpin 360 Design Verification (DV) product line leverages the most advanced, high-performance formal technology as the basis for a range of verification solutions, from automated design analysis to advanced property checking.

»Download the flyer…OneSpin’s Quantify measures the quality of a formal verification test bench. It provides precise, actionable information on what parts of the design-under-test (DUT) are verified, and it highlights RTL code that could still hide bugs.

»Download the data sheet…OneSpin’s Connectivity XL App is the industry’s first and only solution for the efficient specification and formal verification of huge numbers of deep connections in multi-billion-gate chips.

»Download the data sheet…OneSpin’s VCI App enables users to export structural coverage results produced by OneSpin’s QuantifyTM in different database formats with a single command.

»Download the data sheet…OneSpin 360 DV-Verify adds coverage-driven assertion-based verification (ABV) to the DVInspect platform.

»Download the data sheet…In a systematic verification flow, requirements tracking and coverage play an indispensable role. Generally, this starts from requirements specification, where individual requirements are broken down into features, implementations, verification goals, and metrics.

»Download the data sheet…Design verification has a lot in common with human hygiene practices. The goal of both activities is to remove all dirt, grime, and bugs through an active process of establishing good hygiene.

»Download the white paper…Fault-tolerant hardware development is no longer a niche and presents new challenges. Many engineers face the daunting task of having to examine countless faulty variants of their design in order to integrate and verify multiple safety mechanisms within complex Systems-on-Chip (SoCs).

»Download the white paper…Get in touch!

Learn More About OneSpin's Hetergenous Computing Solutions!

Sven Beyer, Product Manager Design Verification