Automatic and exhaustive analysis of a code base for classic implementation problems

Integrated circuit designers are under constant pressure to deliver bug free code that meets evermore rigorous requirements. It is well known that the more bugs that can be detected early in the development process, the faster and easier that development effort will be. However, early bug detection requires a verification overhead on the designer that can be onerous and impact the design process.

OneSpin 360 DV-Inspect™ takes designers' pain away and automatically and exhaustively analyzes RTL source code prior to functional verification and synthesis, eliminating hard to find implementation errors early in the design process.

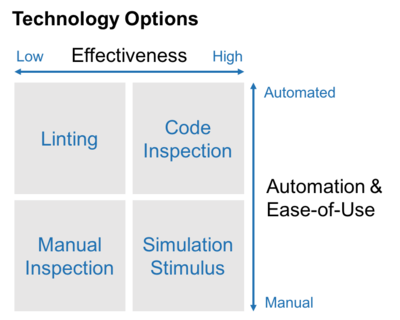

Design Verification Options

The two major methods that designers can leverage to detect bugs are static linting and simulation. Linting requires low set up and can detect a class of bugs based on the syntax of the code, although does tend to report a large number of potential issues that have to be analyzed, and is limited when examining the sequential operation of a block. Simulation is focused on the code operation but requires a greater degree of set up, in the form of directed stimulus creation, which are usually not available at this stage in the process, and will only detect issues in scenarios that the provided stimulus is examining.

What designers require for early and automated detection of implementation issues are, on one hand, fast and easy to set up static checks for the sequential operation of the code in an exhaustive fashion, without relying on user provided stimulus. This is where code inspection with OneSpin 360 DV-Inspect comes in.

Automatic Code Inspection

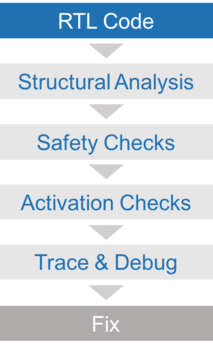

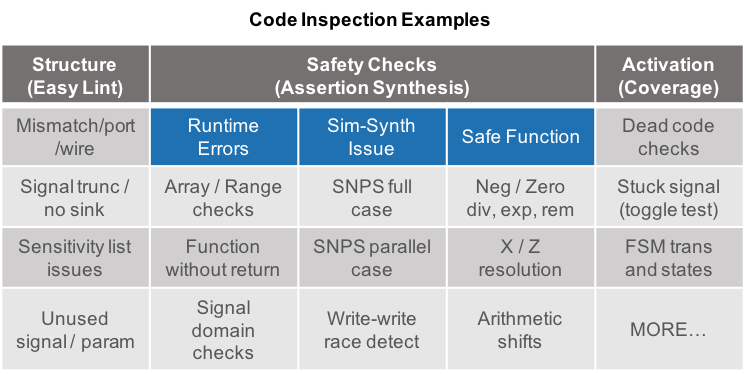

OneSpin 360 DV-Inspect helps to rapidly eliminate errors in a piece of RTL, prior to functional verification and synthesis, while providing a fully automated, and simple use-model. It brings together three powerful Apps, in a single product that all leverage the OneSpin Formal Platform, to driving three different verification perspectives:

- Structural Analysis: Focused syntactic and semantic analysis of source code.

- Safety Checks: Exhaustively verify the absence of common sequential design operation issues and failure debugging.

- Activation Checks: Ensures that specific design functions can be executed and are not blocked by unreachability.

The three apps have one thing in common, they are all fully automatic and require no assertions to be created by the user. As such, DV-Inspect is a push button, automated tool that performs a powerful and complete range of verification functions without the need to learn how to write stimulus, create assertions or understand the formal mechanisms employed. This makes it an invaluable tool for designers to weed out possibly complex design bugs in their code with minimal operational overhead, early in the design process.

General Capabilities

Packaging the three apps into a single tool based on the OneSpin formal platform enables all the advantages of that platform:

360 DV's comprehensive standards compliance allows an easy integration into existing flows. Designs in VHDL, Verilog, SystemVerilog, SystemC or C++ and any combination of these, are fully supported.

Design setup in Inspect is straightforward, allowing its quick and easy adoption into existing flows. For example, existing HDL scripts may be reused and arbitrarily loaded into the tool. The system will take care of appropriate file ordering and automatically detect clocks and reset signals, thus saving time in the definition of these key inputs usually required in most tools. All these mechanisms provide the easy push button approach with minimal or no user interaction.

With 360 DV-Inspect’s network distribution, computationally expensive tasks can be parallelized over a network, accelerating execution. All results are collected in one central place for easy analysis. In essence, the only visible difference between running checks sequentially on a single machine or distributed over the network is the significantly reduced runtime due to parallel execution. This mechanism may be extended by leveraging cloud-based servers through the OneSpin Cloud solution.

In verification, engineers spend most time in debug. Inspect includes a comprehensive, ergonomic debug environment that incorporates various displays including standard waveform windows with signal coloring to highlight cause of failure, a source code window with active value annotation, and active driver tracing that allows accelerated root cause analysis. In addition, the various apps have more specialized displays, such as an FSM analysis tool that highlights problem states. The debugger uses a highly ergonomic Graphical User Interface (GUI) that makes code manipulation a snap.

The OneSpin tool feature witness creation that further eases the understanding of issues. On detection of a problem, the formal platform will create a signal time trace that demonstrates a sequence of events that leads to the problem. This ease of use feature makes the formal process easy to understand by leveraging a familiar waveform approach to visualize issues. Furthermore, the trace may be output as simulation stimulus from reset that allows the problem to be recreated using a standard simulator for further analysis if necessary. This allows an easy connection to the simulation flow and the automatic creation of directed tests.

DV-Inspect runs on both Windows and Linux platforms.

OneSpin 360 DV-Inspect is an invaluable tool for designers and other engineering specialization to discover and solve problems with minimal effort. The tool replaces a substantial amount of simulation by examining code operation for known classic problems, through an exhaustive analysis of source code.

Get in touch!

Eliminate hard to find implementation errors early in the design process and try the OneSpin 360 DV-Inspect on your RTL code now!